详细的 Strix Halo 和 Strix Point 规格表面由官方泄露的 AMD 文件提供

由于大量泄密和谣言,我们对 Strix Point 和 Strix Halo APU 知之甚少。例如,我们最近报告了顶级 Strix Point SKU 的性能。然而,除了透露 Strix APU 将依赖 Zen 5 CPU 和 RDNA 3+ iGPU 之外,AMD 尚未正式确认计算单元数量、缓存大小等细节。

今天,我们似乎拥有了 Strix Point 和 Strix Halo 的官方规格,这要归功于在线发布的 AMD 文件泄露并随后被 HKEPC 发现。

AMD Strix Halo:16 个完整的 Zen 5 核心 + RDNA 3.5

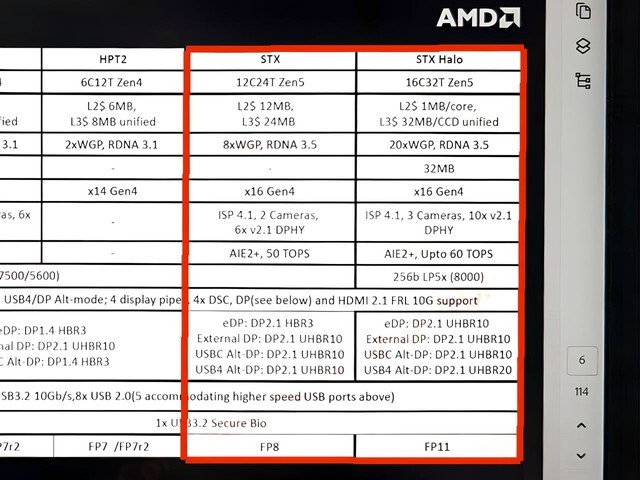

从Strix Halo开始,AMD的下一代旗舰APU显然是基于小芯片的,最高有16个Zen 5内核,分布在两个CCD和32个线程中。每个 CCD 每个内核将有 1 MB 的 L2 缓存和 32 MB 的 L3 缓存。因此,我们正在查看 16 MB 的 L2 和 64 MB 的总 L3 缓存。

据报道,在GPU方面,Strix Halo的RDNA 3.5 iGPU携带20个WGP或40个CU。例如,RX 7600 XT 只有 32 个 CU。为此,泄漏指出 Strix Halo 比 RX 7600 XT(在亚马逊上有售)更快。

此外,似乎还有 32 MB 的 MALL(内存附加的最后一级)缓存。32 MB MALL 缓存的存在对 Strix Halo APU 来说应该是个好兆头,因为 iGPU 经常因为缺乏专用 VRAM 而缺乏内存带宽。

其他值得注意的细节包括支持 LPDDR5X-8000 RAM 和具有高达 60 TOP 计算能力的 NPU。

最后,Strix Halo APU 的功率预算似乎为 70 W,AMD 允许芯片配置为高达 130 W 的 TDP。

AMD Strix Point:采用 Zen 5 + Zen 5c 的混合设计

与 Strix Halo 不同,主流的 Strix Point APU 据称是单片的,并采用混合设计,混合了标准 Zen 5 和较小的 Zen 5c 内核。CPU 显然最高为 12 个内核/24 个线程,每个内核携带 1 MB 的 L2 缓存。总 L3 缓存将有 24 MB。

在图形方面,据报道,RDNA 3+ iGPU 具有 8 个 WGP 或 16 个 CU,没有任何 MALL 缓存。因此,虽然我们可以期待比当前的Radeon 780M更好的性能,但由于其削减性质和带宽限制,Strix Point芯片将远远低于Strix Halo产品。

最后,Strix Point APU 的 NPU 据说只能达到 50 TOP,芯片范围从 45 W 到 65 W。

AMD预计将在今年晚些时候发布Strix Pont APU,可能在6月的Computex上。因此,我们不必等待太久就可以了解 Strix 芯片为市场带来什么样的性能。

来源:IT时代网

IT时代网(关注微信公众号ITtime2000,定时推送,互动有福利惊喜)所有原创文章版权所有,未经授权,转载必究。

创客100创投基金成立于2015年,直通硅谷,专注于TMT领域早期项目投资。LP均来自政府、互联网IT、传媒知名企业和个人。创客100创投基金对IT、通信、互联网、IP等有着自己独特眼光和丰富的资源。决策快、投资快是创客100基金最显著的特点。

热门文章

精彩评论

小何华为现在牛的不只是设备商了,,华为的手机现在也是全球销量不错,国内也算是老大了,之前用小米,,现在都改华为了。。产品确实不错。

小何华为现在牛的不只是设备商了,,华为的手机现在也是全球销量不错,国内也算是老大了,之前用小米,,现在都改华为了。。产品确实不错。 小何三星手机在中国还有市场吗?看看现在满大街的vivo和oppo ,,华为,,小米线下店,,就是知道三星的市场基本没有了。。

小何三星手机在中国还有市场吗?看看现在满大街的vivo和oppo ,,华为,,小米线下店,,就是知道三星的市场基本没有了。。 小何滴滴打车现在也没有之前那么火了,,补贴也少了。。

小何滴滴打车现在也没有之前那么火了,,补贴也少了。。 小何今日头条要把腾讯的地方各频道给霸占了。。

小何今日头条要把腾讯的地方各频道给霸占了。。